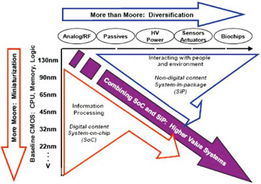

随着集成电路工艺进入纳米尺度,多核与众核处理器成为主流,传统的总线式互连结构在带宽、延迟、可扩展性和功耗等方面面临严峻挑战。片上网络(Network-on-Chip, NoC)作为一种新兴的片上互连技术,以其高带宽、低延迟、良好的可扩展性和功耗效率,成为解决复杂片上系统(SoC)通信瓶颈的关键方案。本文旨在浅析片上网络技术的发展现状与未来趋势。

一、 片上网络技术发展现状

- 架构设计趋于成熟与多样化:目前,NoC的基础拓扑结构(如2D Mesh、Torus、Fat-Tree等)已相对成熟,并在商业多核处理器(如Intel的Teraflops研究芯片、Tilera的TILE系列)中得到应用。研究者们正致力于开发更高效的拓扑,如低直径的蝶形网络、针对特定应用优化的定制化拓扑等。

- 路由算法不断优化:确定性路由(如XY路由)实现简单,但灵活性不足;自适应路由能根据网络拥堵状况动态选择路径,提升吞吐率和均衡负载,是当前研究热点。死锁避免与活锁消除机制也日趋完善。

- 流控机制精细化:从存储转发、虚拟直通到虫孔交换,交换技术不断演进。基于信用的流控和开关注联的虚拟通道技术被广泛采用,以更精细地管理缓冲资源,降低头阻塞影响。

- 与上层应用的协同设计:NoC不再是孤立的通信底板,其设计与任务映射、调度、电源管理、可靠性机制紧密结合。针对人工智能、图像处理等特定领域的专用NoC(Domain-Specific NoC)设计日益受到重视。

- 工艺推动下的新挑战:随着工艺节点持续缩小,互连线延迟和功耗占比增大,信号完整性与可靠性问题(如串扰、老化、软错误)凸显,需要在NoC设计层面引入容错和可靠性增强机制。

二、 片上网络技术发展趋势

- 从2D迈向3D集成:3D集成技术通过硅通孔(TSV)实现芯片的垂直堆叠,为NoC设计带来革命性变化。3D NoC能极大缩短全局互连长度,降低延迟和功耗,是突破带宽和互连密度瓶颈的重要方向。其拓扑、路由和热管理是研究重点。

- 光互连技术的融合:硅光子技术为片上通信提供了超高带宽、超低功耗的潜力。光NoC(ONoC)目前虽在工艺集成、调制器/探测器效率等方面存在挑战,但作为长远发展方向,正吸引大量研究投入,可能在未来实现光电混合甚至全光互连。

- 智能与自适应能力提升:利用机器学习等人工智能技术,使NoC具备在线学习与预测能力,实现智能化的流量预测、拥塞控制、路由选择和功耗管理,构建“认知NoC”,以动态适应多变的工作负载。

- 异构集成与Chiplet互连:在Chiplet(小芯片)设计范式中,不同工艺、功能、供应商的芯粒通过先进的封装技术(如硅中介层)集成。此时,片上网给(Network-in-Package, NiP)或作为其核心的NoC技术,需要解决跨Die的、可能异构的互连问题,标准化接口(如UCIe)与通信协议至关重要。

- 安全性与可信性设计:NoC作为片上所有核心的通信枢纽,其安全脆弱性(如窃听、篡改、拒绝服务攻击)不容忽视。未来NoC设计必须将安全作为原生特性,集成加密、认证、入侵检测等硬件安全机制,构建可信执行环境。

- 设计方法学与工具链完善:随着NoC复杂度提升,需要更高层次的抽象、更强大的建模与仿真工具,以及自动化综合与优化流程,以降低设计门槛,缩短开发周期,支持快速探索不同架构的权衡。

片上网络技术已从学术研究走向工业实践,成为支撑高性能计算、人工智能加速器、通信设备等复杂芯片的基石。面对后摩尔时代的新挑战与新机遇,NoC技术正朝着三维化、光电融合、智能化、安全化和支持异构集成的方向快速发展。持续的技术创新与跨领域协同,将推动片上网络在性能、能效和灵活性上达到新的高度,赋能下一代计算系统的革新。